Od rovnice po logickú funkciu v CPLD

...alebo ako začať s CPLD - Lattice

EdizonTN, 09.04.2010-12:17

Aby tie moje poznámky dávali aj nejakú logiku, navodil som si východzie podmienky:

- potrebujem vytvoriť dvojvstupové logické hradlo AND, v programovateľnom CPLD od Lattice z rady ispMACH4000 (Homepage), konkrétne v čipe LC4032ZC (Datasheet).

- nikdy som nič také na mojom PC nerobil

- hardware neriešim, ale používam originál programovací kábel od Lattice (a aj SW)

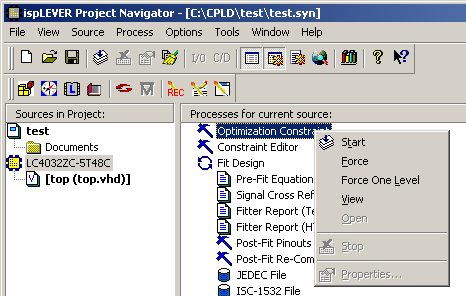

- programovací jazyk bude VHDL

Hardware - Lattice CPLD z rady ispMACH4000: LC4032ZC

Lattice túto architektúru CPLD získal odkúpením konkurenčnej spoločnosti Vantis Corporation (Sunnyvale, California, divízia programovateľných polí AMD).

Mnou použitý čip - LC4032ZC stojí od 2,- USD

ispMACH 4032ZC, 32 MacroCells, 32+4 I/Os,tPD 3.5 ns, tCO 3.0 ns, tS 2.2 ns, fMAX 267 MHz, VCC 1.8V, Max. standby current 20 μA, púzdro: 48-pin TQFP

Toto CPLD používa na napájanie jadra 1.8V. Ďalej disponuje dvoma bankami napájania (BANK1 a BANK2), takže sa dá použiť ako voltage-level converter. Okrem toho, sú všetky I/O 5V tolerantné.

Postup je teda nasledovný.

Získanie softwéru

1.Vytvorím si konto na webe Lattice: https://www.latticesemi.com/account/login.cfm

-- prihlásim sa. Niektoré linky fungujú iba prihláseným užívateľom.

2.a. Základný systém - ispLEVER Classic: (http://www.latticesemi.com/products/designsoftware/isplever/ispleverclassic/index.cfm)

- ispLEVER Classic 1.3 Base Module. Ide o IDE samotné...

-- obsahuje aj driver pre USB/paralel programátor

-- link: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=34444

-- sťahujem

2.b. Pokiaľ plánujem pracovať aj s FPGA-čkami (akože satiaľ nie), doplním inštaláciu o MODUL FPGA: ispLEVER Classic 1.3 FPGA Module

-- Link: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=34445

-- sťahujem

2.c. MODUL syntézy - požiadám o link na aplikáciu syntézy Synplify Synthesis Module

-- tuto: http://www.latticesemi.com/products/designsoftware/isplever/download_request.cfm?p=synplify&pp=classic

-- po obdržaní download linku emailom (do 1 prac.dňa), tento sťahujem (C1.3.00.09.29.09_Synplify.exe)

... už nikdy link nebudem pýtať v piatok poobede. Link ktorý prišiel emailom je aktívny iba 4 hodiny, a úplnou náhodou som ho našiel v pošte (v sobotu aj niečo robím mimo PC ).

).

2.d. Programovací SW - IspVM System 17.7 - programovanie CPLD cez JTAG. Pracuje bez časového obmedzenia.

Pracuje iba s originálnym "Download" káblom od Lattice (a Vantisu, a LPT káblom) (http://www.latticesemi.com/products/developmenthardware/programmingcables.cfm?source=topnav)

-- sw verzia pre Windows: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=8129

-- sw verzia pre Linux: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=25082

-- sťahujem Win verziu.

3. Inštalácia

Nainštalujem stiahnutý softwér. Postupujem tak ako som ho sťahoval, čiže a, b, c, d.

-- Odporúčam ponechať defaultné nastavenie pri inštalácii. Cielenie adresárov nie je síce najšťastnejšie, ale predíte sa tým možným problémom.

4. Získanie Licencie (ispLEVER Classic)

Získať licenciu je treba po inštalácii, alebo po jej expirácii (1x za rok). Pri expirovaní licencie, netreba preinštalovávať celé prostredie, stačí nahradiť licence.dat súbor...

Postup:

- vojdem na web http://www.latticesemi.com/licensing/flexlmlicense.cfm?p=classic

- zistím si MAC adresu sieťového adaptéru (na PC na ktorom je nainštalovaný ispLEVER) príkazom v command lajne: "ipconfig /all"

Túto MAC adresu zadám do webového formulára a potvrdzujem.

- po menšom čakaní, emailom dostávam súbor "licence.dat". Tento nakopírujem do adresára "\licence" v ispLever-i (c:\ispLEVER_Classic1_3\license\).

Týmto mám prostredie pripravené na prácu.

Idem programovať logickú funkciu Y = A and B

Vytvorenie projektu

5. Spustím prostredie ispLever Project Navigator

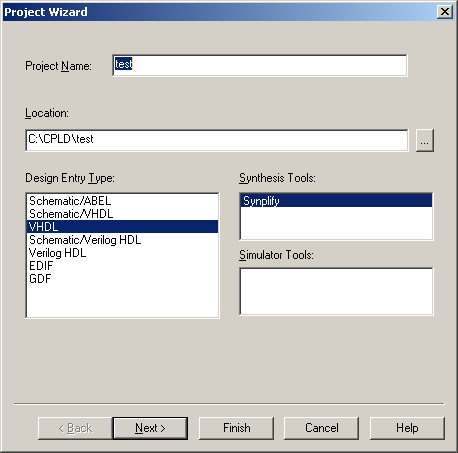

5.a. Vyvtorím projekt. Cez Menu -> File, aktivujem položku "New Project". Spustí sa sprievodca "Project Wizard"

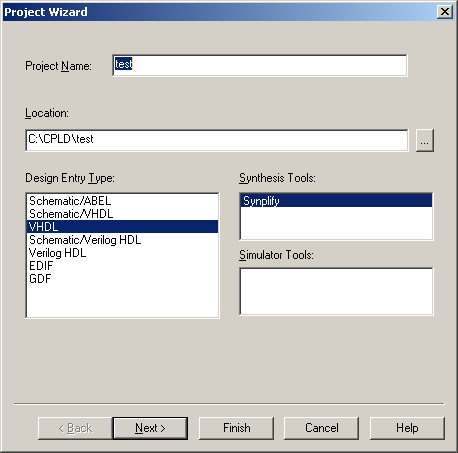

5.b. V prvom okne potrebujem nastaviť názov a adresáre.

V tomto okne si vytvorím názov projektu, a vyberiem typ entry projektu (niečo ako main v C) - VHDL.

Ďalej si môžm vybrať akú syntézu (kompilátor) použijem a aký simulátor. Po inštalácii popísanej vyššie, máme k dispozícii ovšem iba Synplify syntézu, a simulátor nemám k dispozícii (no, dá sa zadarmo stiahnúť, ale nedostal som z neho žiaden výsledok, tak ho nechávam na pokoji).

Tu treba dávať pozor, pri položke "Location", program automaticky NEVYTVÁRA podadresár s názvom projektu! Tento treba dopísať práve do položky location. Po kliknutí na tlačítko "Next", bude tento adresár vytvorený.

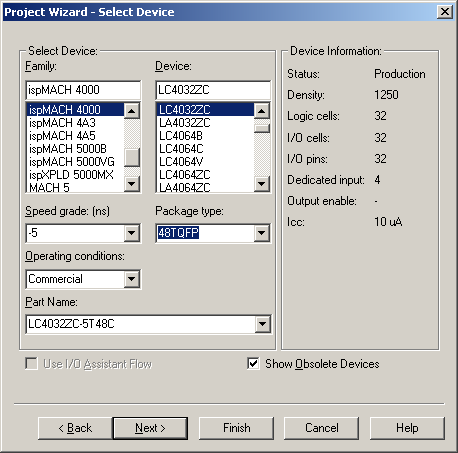

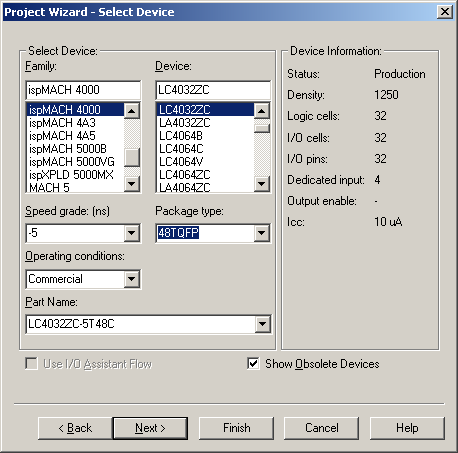

5.c. Project Wizard - Select Device

V tejto časti už definujem, aký konkrétny čip budem programovať. Vyberieme rodinu, typ a ďaľšie parametre.

5.d. "Project Wizard - Add source" sa dajú pridať už existujúce projetové súbory. Žiadne nemám, nič teda nepridám.

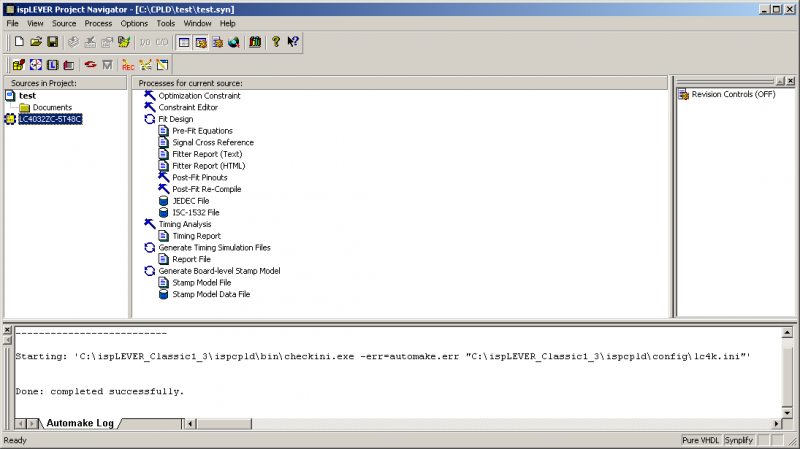

5.e. Teraz sa už iba zobrazia sumárne informácie o vytváranom projekte. Kliknutím na "Finish", program vytvorí celú adresárovú štruktúru projektu, spolu s inicializačným nastavením.

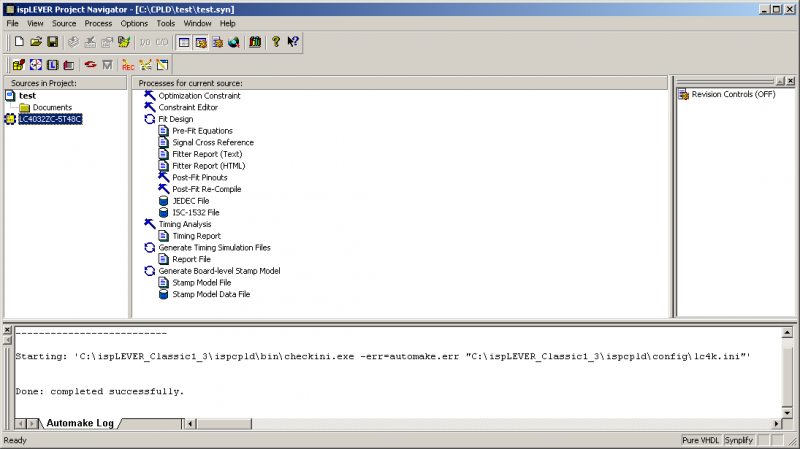

Teraz je projekt vytvorený a môžem začať už konečne programovať.

Kódovanie

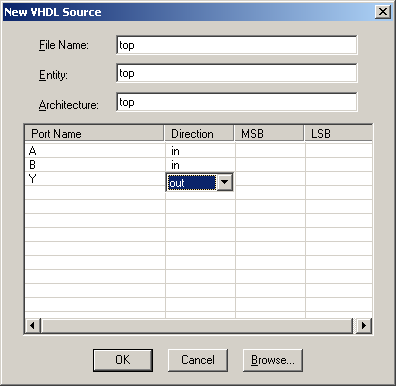

6.a. Pridám Entry pre projekt (vytvorím súbor s MAIN-om). Cez Menu -> Source -> NEW, v ponuke typov vyberám "VHDL mdule".

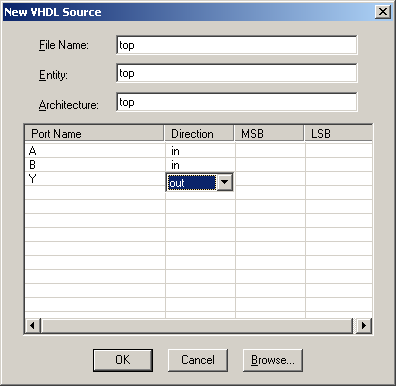

6.b. Následne ma program núti vyplniť informácie o tomto zdrojovom súbore. Zadávam teda názov súboru ("top", u PLD ho zvyknú volať najvrchnejší, nie main), Entity ("top") a Architecture (tiež zadám "top").

V riadkoch PortName,... odo mňa program pýta, definíciu vstupov/výstupov, ktoré bude používať vytváraná entita.

Zadám teda A a B ako Vstup a Y ako výstup. Parametre MSB a LSB nechám zatiaľ na pokoji, tie sú treba pri definovaní zberníc (spodný a horný bit zbernice).

Po Kliknutí na "OK", mi program vygeneroval šablónu zdrojového textu.

Šablóna obsahuje povinné časti ako:

6.c. Z celého CPLD vytvorím jedno AND hradlo (za dva doláre...).

Do architektúry vložím kód, ktorý sa aktivuje pri zmene signálov A a B. Výsledný kód bude vypadať nasledovne:

Po úprave kód uložím (CTRL+S).

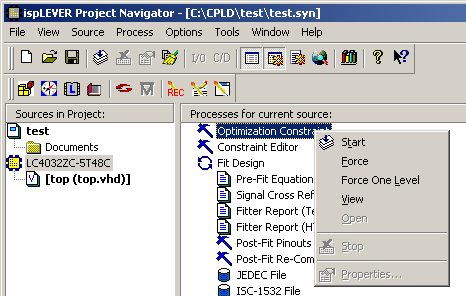

7. Ďaľšie akcie nad CPLD sa vykonávajú výberom v pravej časti Project Navigatora, v sekcii "Processes for current cources, pri vybratom čipe (LC4032ZC-5T48C).

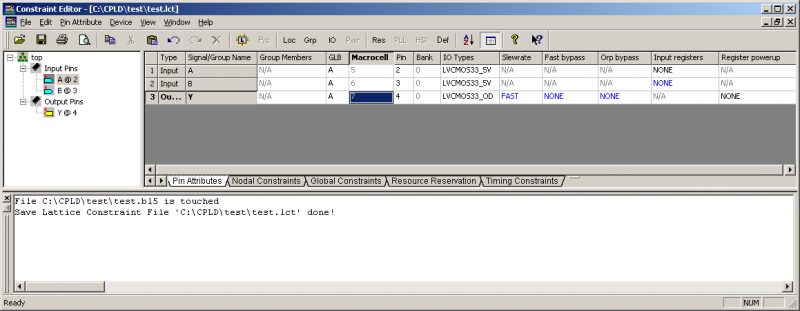

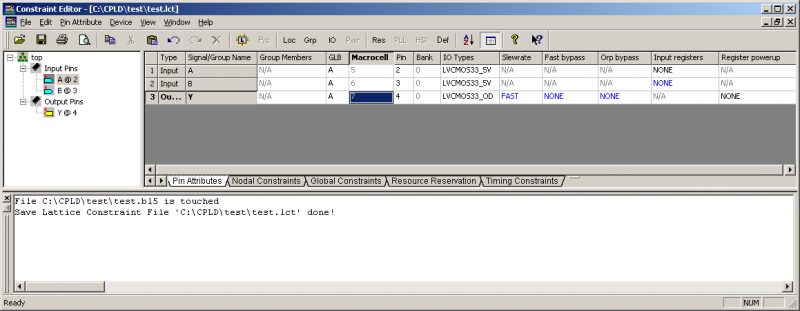

7.a. vyberám "Constrain Editor" - čo je prepojenie fyzických pinov CPLD čipu, s funkčnými PORT-ami vo funkčných blokoch (nadrátovanie pinov CPLD).

Ja musím teda vstypy A a B a výstup Y priradiť fyzickým pinom CPLD.

Pri spustení "Constrain Editor-a" mi najskôr program spustil syntézu. Ak by bol v zdrojovo texte problém, ediutor sa nespustí, a o chybe sa vypíše informácia v spodnej časti "Project Navigatora"

Pri otvorení tohot okna, vidím iba v ľavej časti porty, použité v kóde. Dvojitým poklepaním myškou na konkrétnom porte, sa tento zobrazí v pravej časti okna (ako excel tabuľka), v ktorej sú fyzické piny CPLD.

V tejto časti sa aj nastavujú jednotlivé parametre pinu ako fyzické číslo pinu (Pin), Typ IO pinu (IO Types) a možnosť aktivácie vstupného alebo výstupného registru a pod.

Tak isto môžem zapnúť Pull-Up odpory (v sekcii Nodal Constraints) alebo nastaviť mnohé ďaľšie parametre.

Tak isto, všetky zmeny ukladám cez CTRL+S.

7.b. Následne spúšťam funkciu "FIT design", kde sa mi otestuje rôznymi nástrojmi návrh, čo mi umožní spustenie generovania výstupného súboru pre programátor.

7.c. Po úspešnom zbehnutí "FIT Design", spúšťam teda "JEDEC File", čím dám povel na vygenerovanie ".jed" súboru, ktorý pomocou programátora nahrám do CPLD a ten začne robiť čo chcem.

Výsledkom celého snaženia je súbor "test.jed"

Programovanie

8. Pripájam programátor do USB a k hardwéru, pripojím zdroj a spúšťam programovací sw - ispSystem

9. ako prvé nastavujem typ programovacieho kábla. V Menu -> Options -> :Cable and I/O Port Setup"

9.a. Vyberám "Autodetekciu", ktorá funguje pekne a nachádza mi EzUSB-0 programovací kábel.

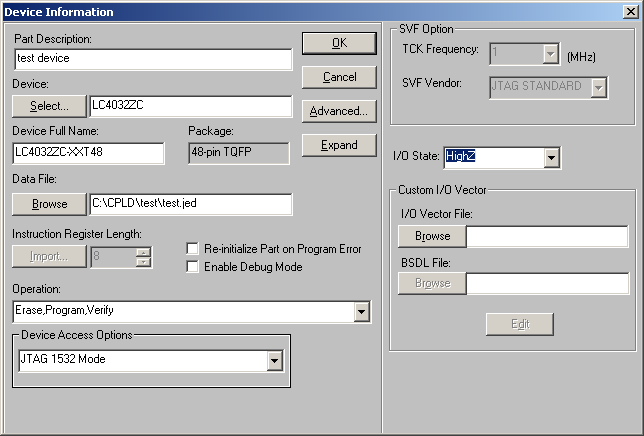

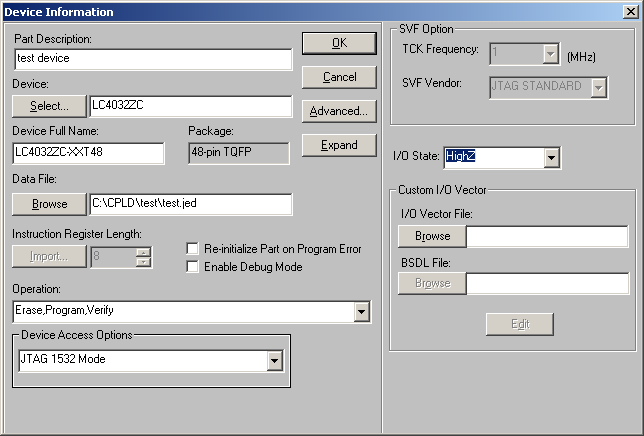

10. Hardware pripravený, teraz vytvorím konfiguračné nastavenie programátora. V Menu volím File -> New.

10.a. Pridám Target Device, cez Menu -> Edit -> "Add Device"

10.b. V tomto okne vyberám Device (LC4032ZC) pomocou tlačítka "Select", a pomocou "Browse" aj Data File, teda vygenerovaný JEDEC súbor (test.jed).

10.c. A spúšťam programovanie CPLD čipu. Menu -> Project - Download.

O necelé 3 sekundy je po všetkom....

Tak som s 48 pinového CPLD, vytvoril dvojvstupové hradlo AND.

Ešte pár zaujímavých linkov:

Pekná stránka nielen o VHDL

http://www.scribd.com/doc/23269/VHDLCookbook

http://www.scribd.com/doc/26992900/Vhdl-Tutorial

tento článok je z mikroZONE

( https://mikrozone.sk/pluginy/content/content.php?content.46 )

...alebo ako začať s CPLD - Lattice

EdizonTN, 09.04.2010-12:17

- potrebujem vytvoriť dvojvstupové logické hradlo AND, v programovateľnom CPLD od Lattice z rady ispMACH4000 (Homepage), konkrétne v čipe LC4032ZC (Datasheet).

- nikdy som nič také na mojom PC nerobil

- hardware neriešim, ale používam originál programovací kábel od Lattice (a aj SW)

- programovací jazyk bude VHDL

Hardware - Lattice CPLD z rady ispMACH4000: LC4032ZC

Lattice túto architektúru CPLD získal odkúpením konkurenčnej spoločnosti Vantis Corporation (Sunnyvale, California, divízia programovateľných polí AMD).

Mnou použitý čip - LC4032ZC stojí od 2,- USD

ispMACH 4032ZC, 32 MacroCells, 32+4 I/Os,tPD 3.5 ns, tCO 3.0 ns, tS 2.2 ns, fMAX 267 MHz, VCC 1.8V, Max. standby current 20 μA, púzdro: 48-pin TQFP

Toto CPLD používa na napájanie jadra 1.8V. Ďalej disponuje dvoma bankami napájania (BANK1 a BANK2), takže sa dá použiť ako voltage-level converter. Okrem toho, sú všetky I/O 5V tolerantné.

Postup je teda nasledovný.

Získanie softwéru

1.Vytvorím si konto na webe Lattice: https://www.latticesemi.com/account/login.cfm

-- prihlásim sa. Niektoré linky fungujú iba prihláseným užívateľom.

2.a. Základný systém - ispLEVER Classic: (http://www.latticesemi.com/products/designsoftware/isplever/ispleverclassic/index.cfm)

- ispLEVER Classic 1.3 Base Module. Ide o IDE samotné...

-- obsahuje aj driver pre USB/paralel programátor

-- link: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=34444

-- sťahujem

2.b. Pokiaľ plánujem pracovať aj s FPGA-čkami (akože satiaľ nie), doplním inštaláciu o MODUL FPGA: ispLEVER Classic 1.3 FPGA Module

-- Link: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=34445

-- sťahujem

2.c. MODUL syntézy - požiadám o link na aplikáciu syntézy Synplify Synthesis Module

-- tuto: http://www.latticesemi.com/products/designsoftware/isplever/download_request.cfm?p=synplify&pp=classic

-- po obdržaní download linku emailom (do 1 prac.dňa), tento sťahujem (C1.3.00.09.29.09_Synplify.exe)

... už nikdy link nebudem pýtať v piatok poobede. Link ktorý prišiel emailom je aktívny iba 4 hodiny, a úplnou náhodou som ho našiel v pošte (v sobotu aj niečo robím mimo PC

).

).2.d. Programovací SW - IspVM System 17.7 - programovanie CPLD cez JTAG. Pracuje bez časového obmedzenia.

Pracuje iba s originálnym "Download" káblom od Lattice (a Vantisu, a LPT káblom) (http://www.latticesemi.com/products/developmenthardware/programmingcables.cfm?source=topnav)

-- sw verzia pre Windows: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=8129

-- sw verzia pre Linux: http://www.latticesemi.com/dynamic/view_document.cfm?document_id=25082

-- sťahujem Win verziu.

3. Inštalácia

Nainštalujem stiahnutý softwér. Postupujem tak ako som ho sťahoval, čiže a, b, c, d.

-- Odporúčam ponechať defaultné nastavenie pri inštalácii. Cielenie adresárov nie je síce najšťastnejšie, ale predíte sa tým možným problémom.

4. Získanie Licencie (ispLEVER Classic)

Získať licenciu je treba po inštalácii, alebo po jej expirácii (1x za rok). Pri expirovaní licencie, netreba preinštalovávať celé prostredie, stačí nahradiť licence.dat súbor...

Postup:

- vojdem na web http://www.latticesemi.com/licensing/flexlmlicense.cfm?p=classic

- zistím si MAC adresu sieťového adaptéru (na PC na ktorom je nainštalovaný ispLEVER) príkazom v command lajne: "ipconfig /all"

Túto MAC adresu zadám do webového formulára a potvrdzujem.

- po menšom čakaní, emailom dostávam súbor "licence.dat". Tento nakopírujem do adresára "\licence" v ispLever-i (c:\ispLEVER_Classic1_3\license\).

Týmto mám prostredie pripravené na prácu.

Idem programovať logickú funkciu Y = A and B

Vytvorenie projektu

5. Spustím prostredie ispLever Project Navigator

5.a. Vyvtorím projekt. Cez Menu -> File, aktivujem položku "New Project". Spustí sa sprievodca "Project Wizard"

5.b. V prvom okne potrebujem nastaviť názov a adresáre.

V tomto okne si vytvorím názov projektu, a vyberiem typ entry projektu (niečo ako main v C) - VHDL.

Ďalej si môžm vybrať akú syntézu (kompilátor) použijem a aký simulátor. Po inštalácii popísanej vyššie, máme k dispozícii ovšem iba Synplify syntézu, a simulátor nemám k dispozícii (no, dá sa zadarmo stiahnúť, ale nedostal som z neho žiaden výsledok, tak ho nechávam na pokoji).

Tu treba dávať pozor, pri položke "Location", program automaticky NEVYTVÁRA podadresár s názvom projektu! Tento treba dopísať práve do položky location. Po kliknutí na tlačítko "Next", bude tento adresár vytvorený.

5.c. Project Wizard - Select Device

V tejto časti už definujem, aký konkrétny čip budem programovať. Vyberieme rodinu, typ a ďaľšie parametre.

5.d. "Project Wizard - Add source" sa dajú pridať už existujúce projetové súbory. Žiadne nemám, nič teda nepridám.

5.e. Teraz sa už iba zobrazia sumárne informácie o vytváranom projekte. Kliknutím na "Finish", program vytvorí celú adresárovú štruktúru projektu, spolu s inicializačným nastavením.

Teraz je projekt vytvorený a môžem začať už konečne programovať.

Kódovanie

6.a. Pridám Entry pre projekt (vytvorím súbor s MAIN-om). Cez Menu -> Source -> NEW, v ponuke typov vyberám "VHDL mdule".

6.b. Následne ma program núti vyplniť informácie o tomto zdrojovom súbore. Zadávam teda názov súboru ("top", u PLD ho zvyknú volať najvrchnejší, nie main), Entity ("top") a Architecture (tiež zadám "top").

V riadkoch PortName,... odo mňa program pýta, definíciu vstupov/výstupov, ktoré bude používať vytváraná entita.

Zadám teda A a B ako Vstup a Y ako výstup. Parametre MSB a LSB nechám zatiaľ na pokoji, tie sú treba pri definovaní zberníc (spodný a horný bit zbernice).

Po Kliknutí na "OK", mi program vygeneroval šablónu zdrojového textu.

Šablóna obsahuje povinné časti ako:

- Library: použité knižnice prvkov pre syntézu

- entity : definícia funkčného logického bloku. V ňom ďalej definujem fyzické piny (Port).

- architecture: blok jednotlivých akcií (procesov)

6.c. Z celého CPLD vytvorím jedno AND hradlo (za dva doláre...).

Do architektúry vložím kód, ktorý sa aktivuje pri zmene signálov A a B. Výsledný kód bude vypadať nasledovne:

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_arith.all;

- use ieee.std_logic_unsigned.all;

- entity top is

- port(

- A: in std_logic ;

- B: in std_logic ;

- Y: out std_logic );

- end;

- architecture top of top is

- begin

- p_Y:

- process (A,B)

- begin

- Y <= A and B;

- end process;

- end top;

Po úprave kód uložím (CTRL+S).

7. Ďaľšie akcie nad CPLD sa vykonávajú výberom v pravej časti Project Navigatora, v sekcii "Processes for current cources, pri vybratom čipe (LC4032ZC-5T48C).

7.a. vyberám "Constrain Editor" - čo je prepojenie fyzických pinov CPLD čipu, s funkčnými PORT-ami vo funkčných blokoch (nadrátovanie pinov CPLD).

Ja musím teda vstypy A a B a výstup Y priradiť fyzickým pinom CPLD.

Pri spustení "Constrain Editor-a" mi najskôr program spustil syntézu. Ak by bol v zdrojovo texte problém, ediutor sa nespustí, a o chybe sa vypíše informácia v spodnej časti "Project Navigatora"

Pri otvorení tohot okna, vidím iba v ľavej časti porty, použité v kóde. Dvojitým poklepaním myškou na konkrétnom porte, sa tento zobrazí v pravej časti okna (ako excel tabuľka), v ktorej sú fyzické piny CPLD.

V tejto časti sa aj nastavujú jednotlivé parametre pinu ako fyzické číslo pinu (Pin), Typ IO pinu (IO Types) a možnosť aktivácie vstupného alebo výstupného registru a pod.

Tak isto môžem zapnúť Pull-Up odpory (v sekcii Nodal Constraints) alebo nastaviť mnohé ďaľšie parametre.

Tak isto, všetky zmeny ukladám cez CTRL+S.

7.b. Následne spúšťam funkciu "FIT design", kde sa mi otestuje rôznymi nástrojmi návrh, čo mi umožní spustenie generovania výstupného súboru pre programátor.

7.c. Po úspešnom zbehnutí "FIT Design", spúšťam teda "JEDEC File", čím dám povel na vygenerovanie ".jed" súboru, ktorý pomocou programátora nahrám do CPLD a ten začne robiť čo chcem.

Výsledkom celého snaženia je súbor "test.jed"

Programovanie

8. Pripájam programátor do USB a k hardwéru, pripojím zdroj a spúšťam programovací sw - ispSystem

9. ako prvé nastavujem typ programovacieho kábla. V Menu -> Options -> :Cable and I/O Port Setup"

9.a. Vyberám "Autodetekciu", ktorá funguje pekne a nachádza mi EzUSB-0 programovací kábel.

10. Hardware pripravený, teraz vytvorím konfiguračné nastavenie programátora. V Menu volím File -> New.

10.a. Pridám Target Device, cez Menu -> Edit -> "Add Device"

10.b. V tomto okne vyberám Device (LC4032ZC) pomocou tlačítka "Select", a pomocou "Browse" aj Data File, teda vygenerovaný JEDEC súbor (test.jed).

10.c. A spúšťam programovanie CPLD čipu. Menu -> Project - Download.

O necelé 3 sekundy je po všetkom....

Tak som s 48 pinového CPLD, vytvoril dvojvstupové hradlo AND.

Ešte pár zaujímavých linkov:

Pekná stránka nielen o VHDL

http://www.scribd.com/doc/23269/VHDLCookbook

http://www.scribd.com/doc/26992900/Vhdl-Tutorial

tento článok je z mikroZONE

( https://mikrozone.sk/pluginy/content/content.php?content.46 )